| 防爆指令簡介 | ||||||||||||||

1、指令94/9/EC (新方法) 1994年3月23日,歐洲委員會採用了「潛在爆炸環境用的設備及保護系統」(94∕9∕EC)指令。這個指令覆蓋了礦井及非礦井設備,與以前的指令不同,它包括了機械設備及電氣設備,把潛在爆炸危險環境擴展到空氣中的粉塵及可燃性氣體、可燃性蒸氣與薄霧。該指令是通常稱之為ATEX 100A的「新方法」 指令,即現行的ATEX防爆指令。它規定了擬用於潛在爆炸性環境的設備要應用的技術要求--基本健康與安全要求和設備在其使用範圍內投放到歐洲市場前必須採用的合格評定程序。 它是以法語「Atmosphere Explosible」命名的。 擬用於潛在爆炸危險環境的設備的製造商,應用ATEX指令條款並貼附CE標誌,不用考慮應用其它更多的要求就可以在歐洲任何地方銷售其防爆設備。該指令適用的設備範圍特別大,大致上包括固定的海上平台、石化廠、麵粉磨坊以及其它可能存在潛在爆炸性環境的場所適用的設備。在歐洲市場每年估計採購30億歐元這樣的設備。 概括的說,應用該指令有三個前提條件:

依下列原則將可能存在爆炸性環境之場所劃分成不同危險區(Zones):

由於這些國家規定條款直接由製造商採用,所以首先建議製造商與相應的國家聯繫處討論他們可能遇到的有關指令的任何問題。 所有涉及到的部門的良好合作,正式的ATEX常務委員會已經將一個沒有異議的確定意見形成一套指導記錄(備忘錄)由委員會出版,用於幫助需要應用指令的部門。雖然它不是「法律」並且同樣的沒有法律的效力,但它已經被認識到是非常有用的文檔。由於要求所有這樣的文檔連續修訂,並且也以提供「澄清說明單」的方法來做這項工作。這些說明單是在專家組深入討論後的結果。因此建議相關者留意這兩套咨詢文本,同時還要注意製造商或其它責任人依據指令條款的規定繼續負有的責任。 取材自網路 |

可重複程式設計的晶片,其靈活度就如同處理器系統上執行的軟體,卻不受處理器核心數量的限制。與處理器不同的是,FPGA 本身即為平行架構,因此不同的處理作業並不會佔用相同資源。各個獨立處理作業均將指派至專屬的晶片區塊,不會影響其他邏輯區塊即可自動運作。因此,當要新增其他處理作業時,亦不致影響其他部分的效能。

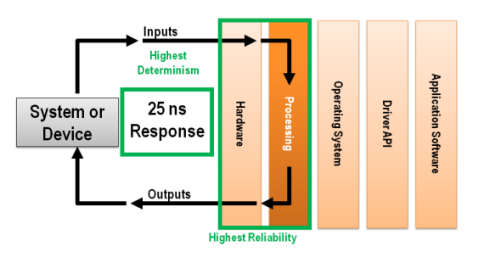

圖 1. FPGA 對處理器架構系統的優勢之一,即是於硬體電路中建構應用邏輯,而不是在作業系統、驅動程式、應用軟體上執行。

若剛接觸 FPGA 的概念,則此篇技術文章將針對「非數位硬體」工程師而介紹 FPGA 的基本概念,與可重設晶片的設計工具。

1. 定義 FPGA 的元件

所有 FPGA 晶片均是透過可程式化的互連 (Interconnect) 機制,銜接有限的預先定義資源所組成,進而建構可重設數位電路與 I/O 區塊,讓電路可聯繫外部世界。

圖 2. FPGA 各個不同的部分

FPGA 一般資源規格包含多組可設定的邏輯區塊、固定的函式邏輯區塊 (如 Multiplier)、記憶體資源的體積 (如嵌入式 Block RAM)。FPGA 晶片仍有許多其他部分。但若要選擇並比較特殊應用的 FPGA,則上述 3 項為最重要的部分。

可設定邏輯區塊 (Configurable logic block,CLB),為 FPGA 的基礎邏輯單位。CLB 有時代表晶片分割 (Slice) 或邏輯單元 (Logic cell),主要由 2 種基本元件所構成:正反器 (Flip-flop) 與查找表 (LUT)。不同 FPGA 的 Flip-flop 與 LUT 封裝方式亦有所差異,所以應先了解 Flip-flop 與 LUT。

接著可進一步了解各項元件。

進一步了解 Flip-Flop

正反器 (Flip-Flop)

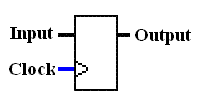

圖 3. 正反器 (Flip-Flop) 的代表符號

Flip-flop 為二進位移位暫存器 (Shift register),可於 FPGA 電路中同步化邏輯,並儲存時脈週期之間的邏輯狀態。在各個時脈緣 (Clock edge) 中,正反器將於輸入通道上鎖存 1 或 0 (TRUE 或 FALSE) 數值,並維持該數值到下個時脈緣。

進一步了解查找表 (LUT)

查找表 (LUT)

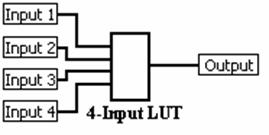

圖 4. 共 4 組輸入的 LUT

CLB 中的大部分邏輯,均是以 LUT 形式的極少量 RAM 所建構而成。因此可假設 FPGA 中的系統閘數量,即等於特定晶片中的 NAND 閘與 NOR 閘數量。但在實際情況下,所有組合邏輯 (Combinatorial logic,即如 AND、OR、NAND、XOR 等) 均於 LUT 記憶體中建構為真值表。真值表 (Truth table) 是針對輸入的各種組合,所預先定義的輸出列表。

這裡先快速複習數位邏輯類別 (Digital logic class)。

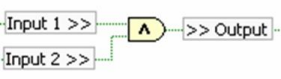

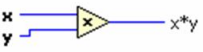

以圖 5 為例,即呈現了 Boolean AND 的作業:

圖 5. NI LabVIEW 的 Boolean AND 作業

針對此 AND 作業的 2 組輸入,其所對應的真值表顯示於表 2 中。

進一步了解 Multiplier 與 DSP Slice

乘法器 (Multiplier) 與 DSP 分割 (Slice)

圖 6. NI LabVIEW 的 Multiply 函式

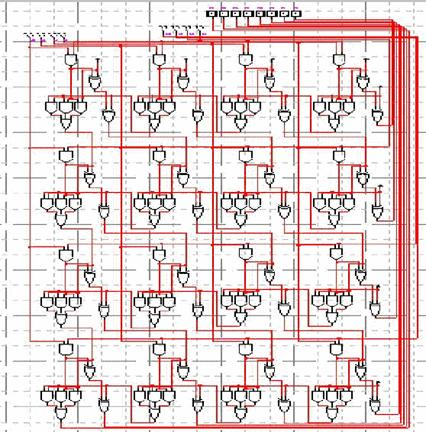

此看似簡單的 2 個數字相乘,卻可能佔用極大量的系統資源,並可建置複雜的數位電路。若需此架構的相關參考,則可觀看圖 6 繪製的電路簡圖,即以組合邏輯建置 4-bit x 4-bit 的乘法器。

圖 7. 4-Bit x 4-Bit 乘法器簡圖繪製

現在先想像相乘 2 組 32-bit 的數字,則單一相乘作業可達超過 2000 個作業。有鑑於此,FPGA 即預先建立了乘法器電路,以於數學與訊號處理應用中減少使用 LUT 與 Flip-flop。

許多訊號處理演算法,均必須持續執行總數字的相乘作業。也因此,較高效能的 FPGA (如 Xilinx Virtex-5),均預先建立了乘法累加 (Multiplier-accumulate) 電路。這些預先建立的處理區塊,亦所謂的 DSP48 分割,即整合了 1 組 25-bit x 18-bit 乘法器與加法器 (Adder) 電路。

進一步了解 Block RAM

Block RAM

當選擇 FPGA 時,記憶體資源亦為重要規格。使用者定義的 RAM 即嵌入於 FPGA 晶片中,可於在平行作業之間儲存資料集或傳輸數值。根據 FPGA 產品的不同,使用者可依 16 或 36 kb 區塊,設定內建的 RAM。當然亦可使用正反器,將資料集建置為陣列;但大型陣列將佔用大量的 FPGA 邏輯資源。1 組 32-bit 的 100-element 陣列,可換算於 Virtex-II 1000 FPGA 中佔用 30% 以上的 Flip-flop;或佔用不到 1% 的嵌入式 Block RAM。DSP 訊號處理演算法,通常必須追蹤完整的資料區塊,或追蹤複雜方程式的係數。但若沒有內建記憶體,許多處理函式並不適於搭配 FPGA 晶片中的可設定邏輯。

FPGA 既有的平行執行功能,可讓不同區塊個別駕馭獨立的硬體邏輯片段。若要於邏輯之間達到不同的資料傳輸速度,其難度頗高;而此時可選用內建記憶體,透過 FIFO 記憶體緩衝區而加快傳輸作業。

2. 為系統設計 FPGA

在了解 FPGA 的基礎元件之後,就可發現於硬體電路中建置邏輯的優點:可確實提升執行的速度、穩定度、靈活度。但因為系統僅依賴 FPGA 進行處理作業與 I/O 連結功能,所以仍須考量其他的優缺點。與「微處理器搭配作業系統 (OS)」的架構相較,FPGA 並不具備完善的驅動程式與 Code/IP 基礎。此外,若以微處理器搭配 OS,即已提供最基礎的檔案結構與多項週邊通訊功能 (如必備的磁碟儲存資料作業)。

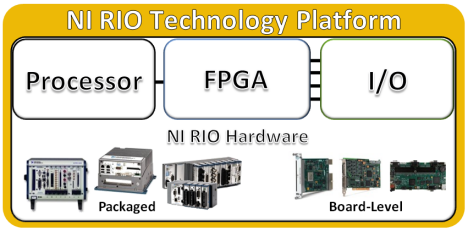

也因此,混合架構亦所謂的異質 (Heterogeneous) 架構,即以微處理器搭配 FPGA 再銜接 I/O,並於最近 10 多年來蓬勃發展。此方式可同時享有利用此 2 種系統的優點。在最近幾年來,如 Xilinx 公司與其 Zynq 系列產品,即以單一晶片整合處理器與 FPGA 的混合式架構,提供相關的解決方案。

圖 8. NI 提供完整的 RIO 系列產品,且封裝式與機板層級的規格均有;讓使用者可透過 LabVIEW 而程式設計此「FPGA 搭配微處理器」的混合架構。

而在最近的 9 年內,NI 亦於其可重設 I/O (RIO) 介面卡上,搭載了強大的微處理器與 FPGA。這些介面卡亦提供多樣規格,且不論是高效能或堅固耐用的系統,均具備相同的 RIO 架構。

3. FPGA 設計工具

在初步了解 FPGA 晶片之後,可能有人會問:「那又要怎麼設計這些數以百萬計的元件,才能建立所要執行的邏輯呢?」

使用者可透過開發工具,於軟體中定義數位運算系統 (Digital Computing Task),再將之編譯為組態檔案或位元流 (Bitstream),並可納入元件接線的相關資訊。在此之前,工程師必須深入了解數位硬體設計,才能使用初階的 FPGA 設計工具;此亦造成了 FPGA 技術的使用挑戰。但如 NI LabVIEW 系統設計軟體的高階合成 (High-level synthesis,HLS) 設計工具問世,進而改變了 FPGA 程式設計的規則;且其提供的新技術,更可將圖形化的程式圖轉為數位硬體電路。

傳統的 FPGA 設計工具

在 FPGA 發展的前 20 年中,如 VHDL 與 Verilog 的硬體描述語言 (HDL) 均演變成主要的程式語言,所撰寫的演算法均用於 FPGA 晶片上。這些初階程式語言,具備其他文字式語言的數項優點,並進一步反應在 FPGA 之上,以利架構出自己所需的電路。而這種混合式語法需比對訊號,或將訊號從外接 I/O 通訊埠連至內部訊號;基本上所銜接的函式本身就已容納該演算法。這些函式將依序執行,並可參照 FPGA 中的其他函式。但在序列式的 Line-by-Line 流程中,其實難以呈現 FPGA 既有的平行執行機制。HDL 雖然具備其他文字式語言的某些屬性,但因為 HDL 屬於資料流模式 (即 I/O 透過訊號連至一系列的函式區塊),所以本質上即有其差異。

接著來看 FPGA 工程師所撰寫的邏輯。實務上,工程師常常以 HDL 撰寫 Test Bench 以存取周遭 (Wrap around);再插入輸入並檢驗輸出,以測試 FPGA 的設計是否可行。Test Bench 與 FPGA 程式碼均於模擬環境中執行。此環境可設定 FPGA 晶片的硬體時序行為模式,並顯示所有輸出/入訊號,以利工程師完成檢驗測試。與原始 FPGA HDL 所需的建立時間相較,HDL Test Bench 建立程序,還有模擬的執行程序,均需更長的時間。

一旦以 HDL 建立 FPGA 設計並檢驗之後,就必須將之代入「文字架構的邏輯」的編譯工具。接著透過數個複雜步驟,將 HDL 合成為組態檔案或位元流,且必須提供元件的相關接線資訊。在此多個步驟的手動程序中,工程師必須針對使用中的 FPGA 晶片,為其腳位指定對應的訊號名稱。

圖 9. 以 VHDL 設計的簡易計數器 FPGA

此設計流程的最後難題,就是必須以極度不普及的傳統 HDL 進行程式設計。也因此,大多數的工程師與科學家並未採用 FPGA 技術。

高階的合成設計工具

正蓬勃發展中的圖形化 HLS 設計工具 (如 LabVIEW),早已解決了傳統 HDL 設計流程上的某些主要障礙。LabVIEW 程式設計環境即具備平行機制與資料流,更適合於 FPGA 程式設計作業。不論是傳統 FPGA 設計的新手或老手,均可利用 FPGA 技術。此外,因為目前仍沿用著功能元件組塊 (IP),所以 LabVIEW 可將現有的 VHDL 整合至 LabVIEW FPGA 設計之中。

圖 10. 右側為 LabVIEW 系統設計軟體,屬於 FPGA 的高階設計工具。當要建立或調整 VHDL 設計時,可讓工程師省略初階作業較複雜的部分。

若要模擬或檢驗 FPGA 邏輯的行為,LabVIEW 亦可直接於開發環境中提供相關功能。即使不具備 HDL 語言的初階知識,亦可建立 Test Benche 以檢驗自己所設計的邏輯。此外,靈活的 LabVIEW 環境亦可匯出至精確週期模擬工具 (如 Xilinx ISim),以協助進階使用者製作時序與邏輯的模型。

LabVIEW FPGA 編譯工具可自動化編譯程序,只要使用者輕點按鈕,即可接收報表與錯誤資訊,直到編譯程序結束。若時序錯誤起自於自己設計的 FPGA,則 LabVIEW 亦可強調這些重要路徑,以加快除錯程序。

4. 結論

隨著 FPGA 技術的普及,如 LabVIEW 的高階工具、標準微處理器、FPGA RIO 架構也隨著不斷提升,讓 FPGA 更易於讓工程師所用。一旦將程式圖編譯至晶片中執行作業時,仍需注意 FPGA 與其執行的狀況。若要為自己的應用選擇合適的 FPGA 晶片,最好是根據 Flip-flop、LUT、Multiplier、Block RAM 比較並選擇硬體系統。若要達到最精巧的體積與最高速度,當然應徹底了解資源使用情形;於開發期間尤為如此。此篇技術文章並未完整說明 FPGA 的基礎元件。可透過下列資源進一步了解 FPGA 與數位硬體設計。

E27-PAR20

E27-PAR20  E27-PAR30

E27-PAR30